Timing

Listado timing

-

6v - nominal and dynamic on-die termination (odt) for data, strobe, and mask signals - low-power auto self refresh (lpasr) - data bus inversion (dbi) for data bus - on-die vrefdq generation and calibration - dual-rank - on-board i2 serial presence-detect (spd) eeprom - 16 internal banks; 4 groups of 4 banks each - fixed burst chop (bc) of 4 and burst length (bl) of 8 via the mode register set (mrs) - selectable bc4 or bl8 on-the-fly (otf) - fly-by topology - terminated control command and address bus - height mm), w/o heatsink jedec/xmp timing parameters: - jedec/pnp: ddr clv / ddr clv - xmp profile #1: ddr clv2v typical - vddq = 1) row active time (trasmin): ns (min5v typical - vddspd = 2detalles del producto tipo de memoria 8gb 1g x 64-bitddr cl-pin dimm especificaciones cl(idd): 15 cycles row cycle time (trcmin): ns (min) refresh to active/refresh command time (trfcmin): 260ns (min2v typical - vpp - 2) maximum operating power: tbd w* ul rating: 94 v - 0 operating temperature: 0º c to +85º c storage temperature: -55º c to +100º c características - power supply: vdd = 1

$ 1495

-

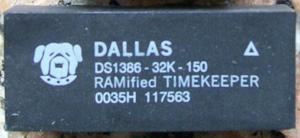

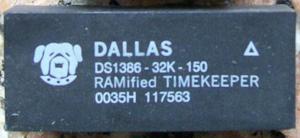

5 v voltage - supply, battery - operating temperature 0°c ~ 70°c mounting type through hole package / case 32-dip module (600 mil), 32-edip + 2 timekeeper m48tpci $ timekeeper dallas dsy $200 realizo envios respondo whatsapptimekeeper dallas dsk description: datasheets ds(p) category integrated circuits (ics) family clock/timing - real time clocks series - type clock/calendar features alarm, leap year, nvsram, square wave output, watchdog timer memory size 32kb time format hh:mm:ss:hh ( hr) date format yy-mm-dd-dd interface parallel voltage - supply 4

$ 200

-

Pc board: formatter board - controls the logic and timing operation of the printer, translates the control panel input codigo: hpi-r-q • consulte stock antes de ofertar • las fotos son genéricas a modo ilustrativo

$ 3991

-

The spd's are programmed to jedec standard latency ddr timing of 9-9-9 at 15v (v ~v) power supply • vddq = 19us at 85°c • asynchronous reset • pcb: height mm), double sided component::::::::: digital general service::::::::::::: somos mercadolíder todo tipo de requerimiento informático san martín - gba envíos a todos el país correo argentino o transporte ===================================the electrical and mechanical specifications are as follows: features • jedec standard 1memoria kingston 8gb ddrmhz, 8gbyte, 2rx8 1gx72-bit, pc modelo: kvrd3e9s/8g description valueram's 1g x 72-bit (8gb) ddr cl9 sdram (synchronous dram), 2rx8, ecc memory modules, based on eighteen 512m x 8-bit fbga components per module8us at lower than tcase 85°c, 35v (v ~ v) • 667mhz fck for mb/sec/pin • 8 independent internal bank • programmable cas latency: • programmable additive latency: 0, cl - 2, or cl - 1 clock • programmable cas write latency(cwl) = 7 (ddr-bit pre-fetch • burst length: 8 (interleave without any limit, sequential with starting address “000” only), 4 with tccd = 4 which does not allow seamless read or write [either on the fly using a12 or mrs] • bi-directional differential data strobe • thermal sensor grade b • internal(self) calibration: internal self calibration through zq pin (rzq: 240 ohm ± 1%) • on die termination using odt pin • average refresh period 7each 240-pin dimm uses gold contact fingers

-

Prácticamente sin uso para entendidos features -sec stopwatch lap 100 x 2 timer • football stopwatch with stoppage time feature • 10-interval timer • 12 alarms • three counter modes standard counter stopwatch counter: counter along with stopwatch timing dual counter: two independent counts • timekeeping function • 5-year battery life • beeper on/off

-

Timekeeper dallas ds1386 - 32k description: datasheets ds1386(p) category integrated circuits (ics) family clock/timing - real time clocks

Argentina

-

The spd is programmed to jedec standard latency mhz timing of 9-9-9 at 1) refresh to active/refresh 160ns (min5v ± v power supply • vddq = 1) command time (trfcmin) row active time (trasmin) 36ns (minthis 240-pin dimm uses gold contact fingers and requires +1a page 1 description this document describes valueram’s m x 72-bit 8gb (mb) ddrmhz cl9 sdram (synchronous dram) registered w/parity, dual-rank memory module, based on thirtysix 512m x 4-bit ddrmhz fbga components) power w (operating) ul rating 94 v - 0 operating temperature 0° c to 85° c storage temperature -55° c to +100° c continued >>the electrical and mechanical specifications are as follows: features • jedec standard 1kvrd3d4r9s/8g 8gb m x 72-bit pc cl9 registered w/parity 240-pin dimm kingston8us at lower than tcase 85°c, 39us at 85°c • asynchronous reset • pcb: height mm), double sided component specifications cl(idd) 9 cycles row cycle time (trcmin) 495v ± v • 667mhz fck for mb/sec/pin • 8 independent internal bank • programmable cas latency: • programmable additive latency: 0, cl - 2, or cl - 1 clock • programmable cas write latency(cwl) = 7(ddr-bit pre-fetch • burst length: 8 (interleave without any limit, sequential with starting address “000” only), 4 with tccd = 4 which does not allow seamless read or write [either on the fly using a12 or mrs] • bi-directional differential data strobe • internal(self) calibration: internal self calibration through zq pin (rzq: 240 ohm ± 1%) • on die termination using odt pin • on-dimm thermal sensor (grade b) • average refresh period 7

-

El secuenciador por pasos permite insertar o eliminar partes al vuelo, utilizando las 16 teclas de pasos para introducir notas mientras recibimos confirmación visual del timing de las notas en el compás dispone de un modo song que permite guardar hasta seis patrones de canciones, cada uno combinando 16 secuenciaspuede sincronizarse con otras unidades a través de la conexión sync, va a pilas, y tiene altavoz incorporadoshow music - instrumentos musicales korg volca sample sampler sequencer digital korg volca sample es un secuenciador de samples que permite editar y secuenciar a tiempo real hasta 100 sonidos muestreadosviene ya con 100 samples precargados, y puedes añadir los tuyos con una app de ios

-

The spds are programmed to jedec standard latency 1066mhz timing of 7-7-7 at 1each 240-pin dimm uses gold contact fingers and requires +1kingston 8gb kit de 2 kvr1066d3q8r7sk2/8g para servidores valueram’s kvr1066d3q8r7sk2/8g is a kit of two 512m x 72-bit 4gb (4096mb) ddr3-1066 cl7 sdram (synchronous dram) registered w/parity, quad-rank memory modules, based on thirty-six 128m x 8-bit ddr3-1066 fbga components per moduletotal kit capacity is 8gb

Argentina

-

Además, incorpora el sistema suzuki racing vvt (variable valve timing system), desarrollado en la gsx-rr de motogpsu rendimiento es mayor y alcanza un régimen de giro superior200 rpm, el motor que la empuja es más compacto que el de su antecesora, lo que ha permitido crear a su alrededor un conjunto más pequeño y ligerosuzuki gsx-r 1000 2018 suzuki gsx-r 1000 uno de los modelos más esperados y se distinguirá por ser la gsx-r más potente y ligera realizada hasta la fechapotencia máxima declarada 202 cv a 13se ha incrementado la potencia y optimizado las dimensiones del motor

Argentina